Kategori: Artikel Pilihan » Elektronik Praktikal

Bilangan pandangan: 12919

Komen pada artikel: 0

Chip 4046 (K564GG1) untuk peranti dengan pengekalan resonans - prinsip operasi

Apabila membuat peranti elektronik kuasa dengan pengekalan resonans dalam litar LC, litar pengawal resonan direka untuk menyegerakkan ayunan yang diterima dengan pulangan kawalan yang datang dari pemandu.

Tugas pengawal ini adalah untuk mengekalkan ayunan bergantian dalam litar LC dengan menariknya pada masa dengan ayunannya sendiri. Untuk mencapai ini, pengawal perlu menerima isyarat dari gelung dari litar yang mengandungi data pada frekuensi semasa dan fasa ayunan bebas di dalamnya, selepas itu, bergantung kepada data ini, mengekalkan tahap pemandu dalam penyegerakan dengan kekerapan dan fasa ini, maka resonans dalam litar akan disimpan secara automatik.

Untuk membina pengawal seperti itu, cip CD4046 atau rakan sejawatannya dalam K564GG1 sesuai. Mari kita lihat peranti microcircuit ini, tujuan kesimpulannya dan rajah sambungan komponen dipasang, untuk memahami, jika perlu, apa yang anda berurusan dengan.

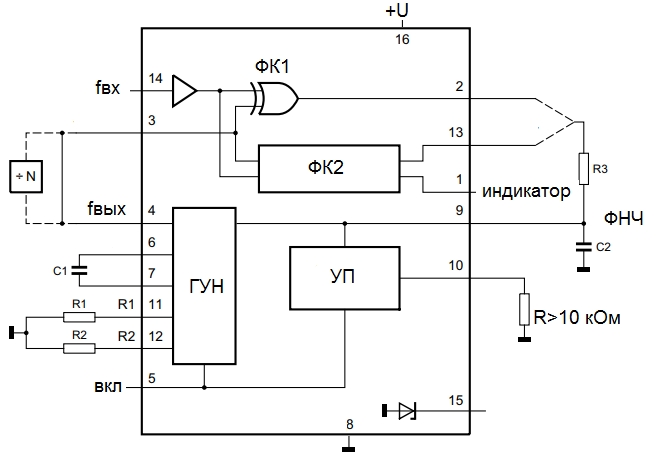

Cip ini membolehkan anda dengan mudah mengatur gelung PLL - fasa terkunci. Untuk membina PLL, tiga blok yang diperlukan digunakan di dalam mikrosirkuit: pengayak dikawal voltan VCO, komparator fasa FC, dan penapis LPF rendah.

Dibina dengan mikroelektrik, VCO menjana urutan denyutan segi empat tepat dengan liputan 50%, iaitu jambatan murni yang kekerapan awalnya bergantung kepada parameter dua litar RC: R1C1 dan R2C2 yang disambungkan ke luar mikroelektrik, dan amplitud dalam kes ini adalah dekat dengan voltan bekalan mikrokitar U +.

Prinsip operasi PLL

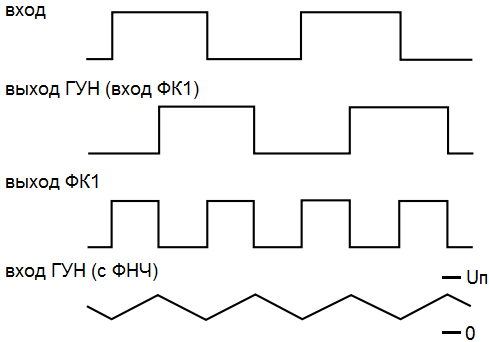

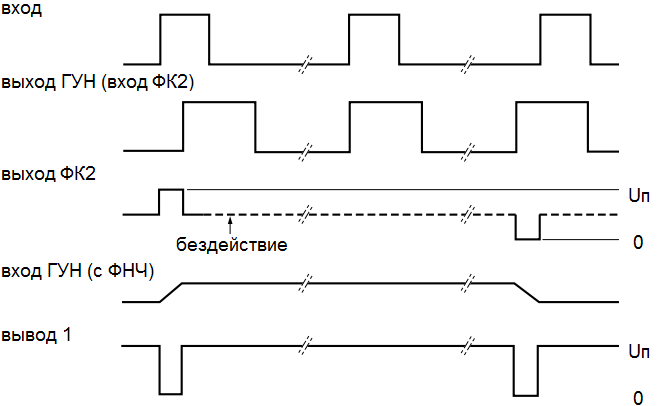

Sirip isyarat input luaran dibekalkan kepada microcircuit, sebenarnya, kepada salah satu input fasa pembanding FC (FC1 atau FC2 - pembangun memilih) di dalamnya. A meander yang dihasilkan oleh VCO secara serentak diberikan kepada input FC kedua. Akibatnya, isyarat segiempat tepat diperolehi pada output FC, tempoh nadi yang bergantung kepada perbezaan antara denyutan dari VCO dan denyutan luaran pada setiap saat.

Malah, tempoh denyutan output dengan FC adalah berkadar dengan perbezaan fasa kedua-dua isyarat berbanding. Faktanya ialah elemen logik eksklusif-OR sering digunakan sebagai FC, ini bermakna bahawa pada output FC akan ada tahap voltan tinggi hanya jika terdapat perbezaan antara isyarat, dan jika tidak ada perbezaan maka output dari FC akan rendah tahap voltan atau keadaan tidak aktif.

Dari keluaran FC, isyarat diberi kepada penapis lulus rendah, iaitu litar RC mudah, pada kapasitor yang voltan ketidakcekapan berdenyut diperolehi, tahap riak berkadaran dengan perbezaan kedua-dua isyarat (dari VCO dalaman dan dibekalkan kepada mikrosirkuit dari luar), sebenarnya perbezaan fasa .

Voltan ketidaksepsi yang diperolehi pada kapasitor LPF segera dimasukkan semula ke input VCO, dan bergantung pada nilai puratanya, kekerapan VCO akan ditala secara automatik supaya kekerapan kilauan pada outputnya fout menghampiri kekerapan isyarat luaran yang datang dari luar mikrosirkuit. Apabila mencapai keadaan sedemikian, voltan purata merentas kapasitor penapis rendah pass akan menjadi yang paling kecil - ini adalah tanda penumpuan maksimum kedua-dua isyarat dalam kekerapan dan fasa. Apabila isyarat itu ditangkap, ia akan terus dipegang oleh gelung PLL.

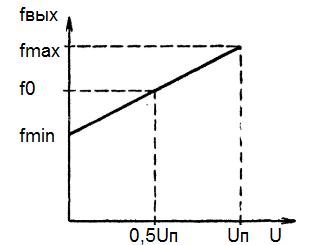

Had penyusunan semula VCO

Seperti yang anda fahami, frekuensi VCO mampu menala dalam julat auto-tuning tertentu. Julat ini ditetapkan oleh komponen luaran cip. Dan kelajuan tindak balas sistem PLL ditentukan oleh pemalar masa LFF (nilai C2 dan R3).Atas sebab ini, anda perlu mendekati pilihan komponen pemasangan cip itu.

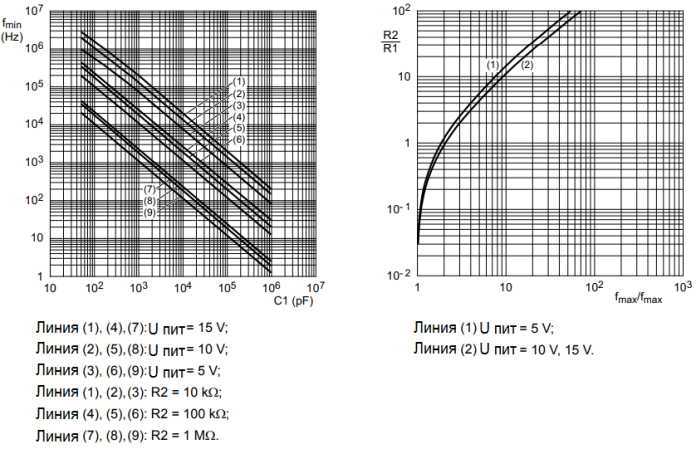

Voltan bekalan microcircuit, kapasitor C1, serta perintang R1 dan R2 menentukan kekerapan VCO frekuensi penalaan diri di dalam microcircuit. Resistor R2 bias fmin frekuensi minimum VCO di atas sifar. Dan nisbah di antara nilai-nilai resistor R1 dan R2 menentukan nisbah antara frekuensi maksimum dan minimum - fmax / fmin, isyarat output yang boleh disesuaikan dari VCO.

Input dan output cip

Kesimpulan 4 - output isyarat daripada VCO, di dalam mod kerja yang meander. Output ini boleh digunakan untuk membekalkan isyarat kepada blok peranti yang direka bentuk.

Pin 5 bertanggungjawab untuk menghidupkan dan mematikan VCO. Apabila voltan paras tinggi digunakan untuk output ini, mikrokircuit akan dimatikan. Apabila memohon tahap voltan rendah (apabila menyambungkan pin 5 kepada dawai biasa) - mikrofon akan berfungsi dalam mod biasa.

Kesimpulan 6 dan 7. Kapasitor C1 disambungkan kepada mereka - ini adalah kapasitor penetapan kekerapan VCO.

Kesimpulan 8 - dawai kuasa biasa cip.

Resistor R1 adalah antara terminal 11 dan wayar biasa. Resistor R2 - antara terminal 12 dan wayar biasa. Ini adalah perintang penentu kekerapan. Resistor R3 daripada penapis rendah pass - untuk pin 9 dan pin 2 atau 13 (perbezaan antara mereka akan dibincangkan kemudian), kapasitor C2 penapis rendah pass antara pin 9 dan wayar biasa.

Pin 10 adalah output penguat repeater. Voltan padanya semasa operasi microcircuit adalah voltan mismatch yang dibekalkan kepada penapis lulus rendah. Kesimpulan 10 direka supaya voltan ketidaksamaan dapat, jika perlu, mudah diasingkan tanpa menghindari kapasitor LPF. Untuk kesimpulan ini, ia dibenarkan untuk menyambung perintang dengan rintangan melebihi 10 kOhm.

Kesimpulan 15 - di atasnya ialah katod terbina dalam zener diode dengan voltan penstabilan 5.6 volt (voltan penstabilan dioda zener ini mungkin berbeza, bergantung kepada pengeluar cip). Diod zener ini boleh digunakan secara pilihan dalam litar kuasa cip.

Kesimpulan 16 - ditambah kuasa cip.

Input dan output pengawal fasa FC1 dan FC2

Rakaman dari output VCO diambil dari terminal 4 dan dimasukkan ke terminal 3, disambungkan melalui penguat penguat kepada input fasa komparator FC1 dan FC2. Sekiranya dikehendaki, isyarat dari VCO boleh dilepaskan melalui pembahagi frekuensi.

Input 14 ialah input isyarat, dan isyarat masukan diberi kepadanya, yang mana perlu untuk menyegerakkan isyarat keluaran pada output VCO. Bergantung pada jenis isyarat masukan, pemaju boleh memilih fasa komparator mana yang hendak digunakan: FC1 atau FC2, dan sambungkan perintang LPF ke comparator yang dipilih (kepada pin 2 atau 13). Fasa komparator FC2 mempunyai indikator pin 1, voltan paras tinggi muncul di atasnya apabila isyaratnya disegerakkan secara maksimum.

Ciri FC1 adalah bahawa ia adalah elemen logik eksklusif-ATAU yang mudah, dan kualiti pengendaliannya bergantung kepada parameter penapis lulus rendah pada outputnya. Kerja bermula dengan frekuensi pusat f0 = (fmax-fmin) / 2, adalah mungkin untuk menangkap harmonik frekuensi pusat. Ia mempunyai imuniti bunyi yang tinggi.

Keanehan FC2 adalah bahawa ia hanya memproses perbezaan positif denyutan yang dibekalkan kepadanya, dan oleh itu kitar tugas denyutan itu tidak penting. Kerja bermula dengan fmin kekerapan minimum, tidak ada kemungkinan untuk menangkap harmonik frekuensi pusat. Ia mempunyai imuniti bunyi rendah. Dalam penapis lulus rendah, kapasitor dengan arus kebocoran rendah diperlukan. FC2 lebih sesuai digunakan dalam litar kuasa dengan resonans LC.

Pemilihan lampiran

Sebagai penapis rendah pass penapis rendah pass, resistor R3 dan kapasitor C2 dipasang. Untuk PLL berfungsi dengan betul, pemalar masa RC mesti puluhan kali lebih besar daripada kekerapan pengambilan PLL.

Sebagai peraturan, kekerapan menangkap kira-kira diketahui oleh pemaju, oleh itu, mereka pada mulanya ditetapkan oleh kekerapan auto-penalaan frekuensi: fmin dan fmax. Nomrogram pertama menentukan, dengan mengambil kira voltan bekalan microcircuit dan fmin yang diperlukan, nilai R2 dan C1.Kemudian, menurut nomogram kedua, berdasarkan nisbah fmax / fmin yang diperlukan, R1 dipilih. Adalah lebih baik untuk memberikan keupayaan untuk menyesuaikan resistor dalam litar.

Lihat juga di i.electricianexp.com

: